## **4V-60V Input Current Mode Synchronous Buck Controller**

#### DESCRIPTION

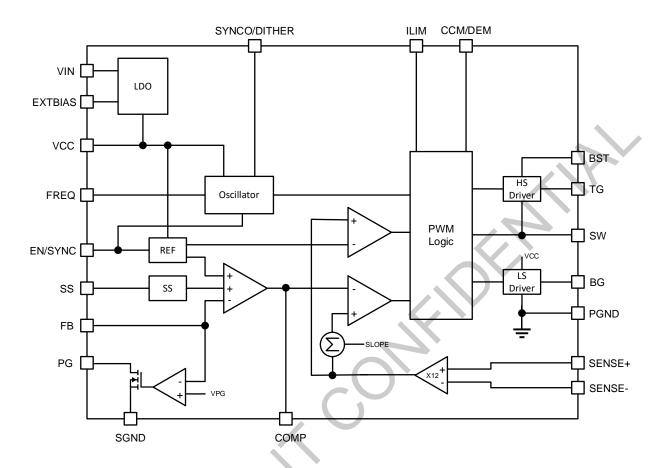

The VE8600 is a high-voltage, synchronous, stepdown controller. The VE8600 uses current mode control with cycle-by-cycle peak valley current limiting or hiccup mode OCP.

The VE8600 has DEM (diode emulation mode) that optimizes light-load efficiency.

The operating frequency of the VE8600 can be programmed by an external resistor or synchronized to an external clock from 100kHz to 1MHz.

The VE8600 offers programmable soft-start and power-good indicator. Full protection features include precision output over-voltage protection (OVP), output over-current protection (OCP), and thermal shutdown.

The VE8600 offers shunt or DCR current sense scheme to detect instant inductor current. The instant peak and valley inductor current limit function is then implemented, which can offer constant current charging for a battery or supper capacitor.

The VE8600 is available in TSSOP20-EP and QFN-20 (3mm x 4mm Wettable Flank) packages. Both packages use EPAD to improve thermal performance and noise immunity. Low pin count, fewer external components, and default internal values make VE8600 an ideal solution for time to market simple power supply design.

Automotive-compliant parts are available under separate datasheet (VE8600Q).

#### **FEATURES**

- Wide 4V to 60V Operating Input Range

- Wide 0.8V to 60V Operating Output Range

- Dual N-Channel MOSFET Driver

- 0.8V Voltage Reference with ±1.5% Accuracy Over Temperature

- Low Dropout Operation: Maximum Duty Cycle at 99.5%

- Programmable Frequency Range: 100kHz - 1MHz

- External Sync Clock Range: 100kHz-1MHz

- 180° Out-of-Phase SYNCO Pin and Dither

- Programmable Soft Start (SS)

- Power Good (PG) Output Voltage Monitor

- Selectable Cycle-by-Cycle Current Limit

- Output Over-Voltage Protection (OVP)

- Hiccup Mode Over-Current Protection

- Peak Valley Current Limit

- Internal LDO with External Power Supply Option

- Programmable CCM and DEM Mode

- Shunt and DCR Sensing

- Low Side FET Ron Sense ZCD

- Available in TSSOP20-EP and QFN-20 (3mm x 4mm Wettable Flank) Packages

#### **APPLICATIONS**

- Automotive

- Industrial

- Renewable energy

- Redundant power supplies

- Robot and drones

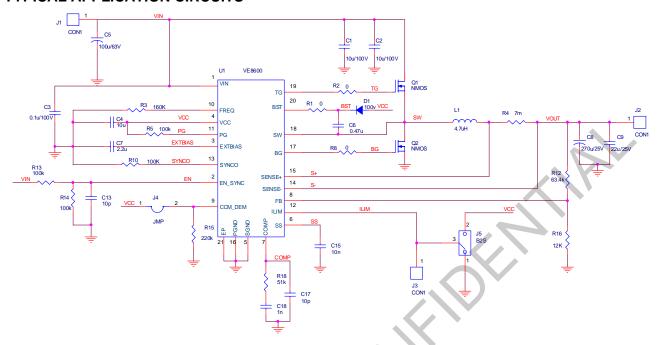

## **TYPICAL APPLICATION**

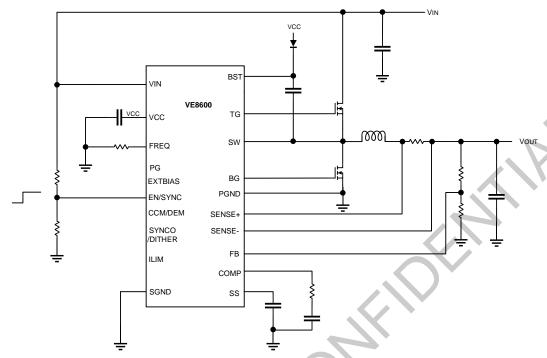

## **Shunt Sensing Application**

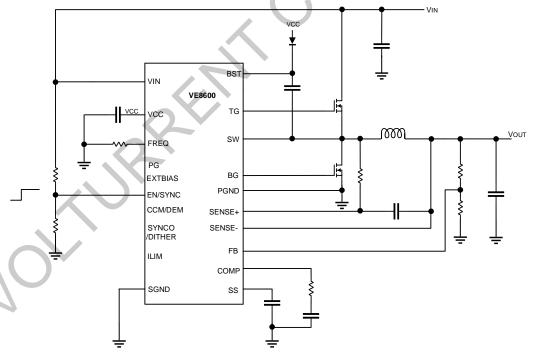

**DCR Sensing Application**

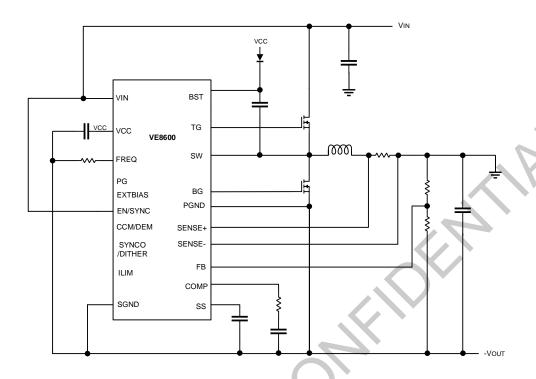

**Shunt Sensing Buck-Boost Application**

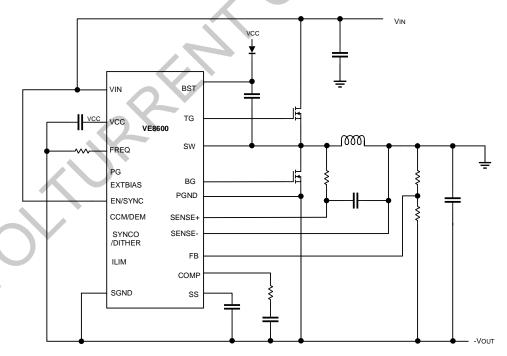

**DCR Sensing Buck-Boost Application**

## **BLOCK DIAGRAM**

## **ORDERING INFORMATION**

| Part Number | Part Marking | Package    | Packing Type                      | Temp Range    |

|-------------|--------------|------------|-----------------------------------|---------------|

| VE8600A5R   | 8600         | TSSOP20-EP | Tape and Reel / Detail in page 24 | -40 to +125°C |

| VE8600AKR   | 8600         | QFN-20     | Tape and Reel / Detail in page 24 | -40 to +125°C |

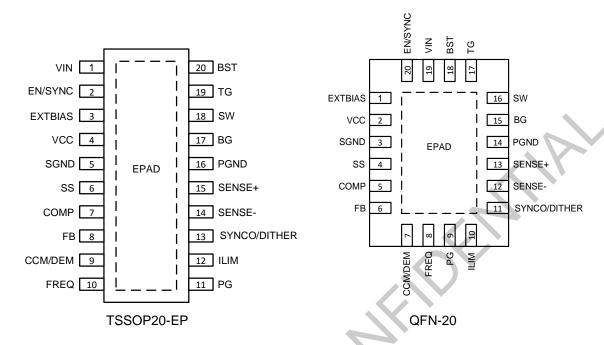

## **PIN CONFIGURATIONS**

## **PIN DESCRIPTION**

| Name    | TSSOP20<br>-EP | QFN-20 | Description                                                             |  |  |  |

|---------|----------------|--------|-------------------------------------------------------------------------|--|--|--|

| VIN     | 1              | 19     | Input supply. This pin should be tied to input rail. Decouple this      |  |  |  |

| V114    | •              | 10     | pin with a small ceramic capacitor to ground.                           |  |  |  |

|         |                |        | <b>Enable input.</b> The threshold is 1.2V with 120mV of hysteresis and |  |  |  |

|         |                |        | is used to implement an input under-voltage lockout (UVLO)              |  |  |  |

| EN/SYNC | 2              | 20     | function externally. If an external sync clock (the frequency is        |  |  |  |

|         |                |        | higher than default frequency set by FREQ) is applied to                |  |  |  |

|         |                |        | EN/SYNC, the internal clock follows the sync frequency.                 |  |  |  |

|         |                |        | External power supply for the internal VCC regulator. EXTBIAS           |  |  |  |

|         |                |        | disables the power from VIN for as long as EXTBIAS is higher than       |  |  |  |

| EXTBIAS | 3              | 1      | 4.7V. Do not connect a power supply greater than 24V to EXTBIAS.        |  |  |  |

|         |                |        | Connect EXTBIAS to an external power supply to reduce power             |  |  |  |

|         |                |        | dissipation and increase efficiency.                                    |  |  |  |

| VCC     | 4              | 2      | Internal bias supply. 5V internal bias supply. A≥4.7µF decoupling       |  |  |  |

| VCC     | 4              | 2      | capacitor is required between VCC and PGND.                             |  |  |  |

| SGND    | 5              | 3      | Low-noise ground reference. SGND should be connected to the             |  |  |  |

| SGND    | 5              | 3      | ground side of the output capacitors.                                   |  |  |  |

| 20      | C              | 4      | Soft-start control input. SS is used to program the soft-start          |  |  |  |

| SS      | 6              | 4      | period with an external capacitor between SS and SGND.                  |  |  |  |

| COMP    | 7              | F      | Regulation control loop compensation. Connect an RC network             |  |  |  |

| COMP    | 7              | 5      | from COMP to SGND to compensate for the regulation control              |  |  |  |

| Name             | TSSOP20<br>-EP | QFN-20 | Description                                                                                                                                                                                                                                                                                |

|------------------|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                |        | loop.                                                                                                                                                                                                                                                                                      |

| FB               | 8              | 6      | <b>Feedback.</b> Connect FB to a resistor voltage divider from the output to ground.                                                                                                                                                                                                       |

| CCM/DEM          | 9              | 7      | Continuous conduction mode/Diode emulation mode (DEM). Floating CCM/DEM or connecting CCM/DEM to VCC makes the part operate in CCM. Connecting an appropriate external resistor from CCM/DEM to SGND makes the part operate in DEM mode. The DEM voltage should be no less than 300mV.     |

| FREQ             | 10             | 8      | <b>Frequency.</b> Connect a resistor between FREQ and SGND to set the switching frequency.                                                                                                                                                                                                 |

| PG               | 11             | 9      | Power good output. The output of PG is an open drain.                                                                                                                                                                                                                                      |

| ILIM             | 12             | 10     | Sense voltage limit set. The voltage at ILIM sets the nominal sense voltage at the maximum output current. There are three fixed options: float, VCC, and SGND.  Connect a resistor or a voltage source that is higher than 0.64V and lower than 1.5V to enable the constant current mode. |

| SYNCO/<br>DITHER | 13             | 11     | <b>Frequency synchronous out.</b> SYNCO outputs a 180° out-of-phase clock when the part works in CCM for dual-channel operation. Connect to GND to enable the dither.                                                                                                                      |

| SENSE-           | 14             | 12     | <b>Negative input for the current sense.</b> The sensed inductor current limit threshold is determined by the status of ILIM.                                                                                                                                                              |

| SENSE+           | 15             | 13     | Positive input for the current sense. The sensed inductor current limit threshold is determined by the status of ILIM.                                                                                                                                                                     |

| PGND             | 16             | 14     | <b>Power ground.</b> Connect PGND directly to the negative terminal of the VCC decoupling capacitor.                                                                                                                                                                                       |

| BG               | 17             | 15     | <b>Bottom gate driver output.</b> Connect BG to the gate of the bottom MOSFET.                                                                                                                                                                                                             |

| SW               | 18             | 16     | <b>Switch node.</b> SW is the reference for the V <sub>BST</sub> supply and high-current returns for the bootstrapped switch.                                                                                                                                                              |

| TG               | 19             | 17     | <b>Top gate drive.</b> TG drives the gate of the top MOSFET. The TG driver draws power from the BST capacitor and returns to SW, providing a true floating drive to the top N-channel MOSFET.                                                                                              |

| BST              | 20             | 18     | <b>Bootstrap.</b> BST is the positive power supply for the high-side MOSFET driver. Connect a bypass capacitor between BST and SW. A Schottky or high-speed diode must be tied from VCC to BST.                                                                                            |

| EPAD             |                |        | <b>Exposed pad.</b> The exposed pad is on the bottom side of device. It is not electrically connected to SGND or PGND. Connect the exposed pad to SGND and PGND during PCB layout for better thermal performance.                                                                          |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter              | Minimum | Maximum | Unit |

|------------------------|---------|---------|------|

| VIN                    | -0.3    | +65     | V    |

| SW                     | -0.3    | +65     | V    |

| SW (transient < 20 ns) | -5      | +65     | V    |

| BST to SW              | -0.3    | VCC+0.3 | V    |

| TG to SW               | -0.3    | VCC+0.3 | V    |

| EN / SYNC              | -0.3    | +65     | V    |

| VCC                    | -0.3    | +6.5    | V    |

| EXTBIAS                | -0.3    | +26     | V    |

| SENSE+-                | -0.3    | +65     | V    |

| SENSE+ to SENSE-       | -0.3    | +0.3    | V    |

| All Other Pins         | -0.3    | VCC+0.3 | V    |

| Junction Temperature   |         | +150    | °C   |

## **ESD RATINGS**

| Parameter                                    | Value | Unit |

|----------------------------------------------|-------|------|

| Human Body Model (HBM), per AEC-Q100-002     | 2     | kV   |

| Charged Device Model (CDM), per AEC-Q100-011 | 1     | kV   |

| Latch-Up, per AEC-Q100-004                   | 100   | mA   |

## THERMAL INFORMATION

| Thermal Resistance | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|--------------------|------------------------|------------------------|

| TSSOP20-EP         | 40                     | 8                      |

| QFN-20             | 48                     | 10                     |

## **RECOMMENDED OPERATINIG CONDITIONS**

| Parameter            | Minimum | Maximum | Unit |

|----------------------|---------|---------|------|

| Temperature          | -40     | +125    | °C   |

| VIN to GND           | +4      | +60     | V    |

| EN / SYNC            | 0       | +60     | V    |

| SENSE+,SENSE- to GND | 0       | +60     | V    |

| EXTBIAS to GND       | +4.7    | +24     | V    |

## **ELECTRICAL CHARACTERISTICS**

V<sub>IN</sub> = 24V, V<sub>EN</sub> = 2V, V<sub>EXTBIAS</sub> = 0V, V<sub>ILIM</sub> = Floating, unless otherwise noted.

| Parameter                                           | Symbol                 | Condition                                                                                                                  | Min   | Тур  | Max      | Unit |

|-----------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------|-------|------|----------|------|

| Input Supply                                        |                        |                                                                                                                            |       | I    | <u> </u> |      |

| V <sub>IN</sub> UVLO threshold (rising)             | VIN_UV_RISING          |                                                                                                                            |       | 4.08 |          | V    |

| V <sub>IN</sub> UVLO threshold (falling)            | VIN_UV_FALLING         |                                                                                                                            |       | 3.78 |          | V    |

| V <sub>IN</sub> UVLO hysteresis                     | V <sub>IN_UV_HYS</sub> |                                                                                                                            |       | 300  |          | mV   |

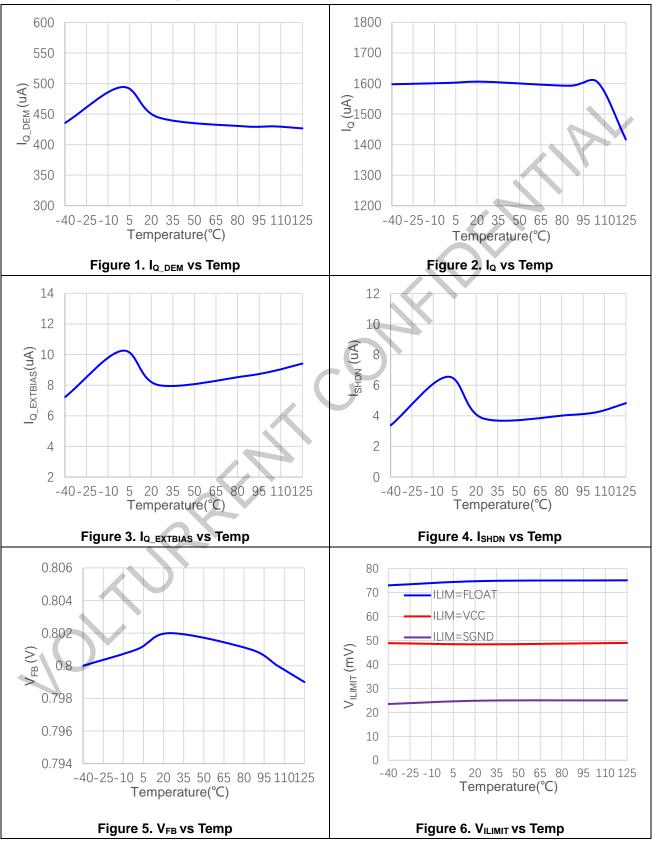

| V <sub>IN</sub> supply current with EXTBIAS bias    | I <sub>Q_EXTBIAS</sub> | EXTBIAS = 12V, $V_{CCM/DEM}$ = 5V, $V_{FB}$ = 0.84V, SENSE+ = SENSE- = 0V, no switching                                    |       | 10   |          | μΑ   |

| V <sub>IN</sub> supply current without EXTBIAS bias | lα                     | EXTBIAS = 0V, $V_{FB}$ = 0.84V, $V_{CCM/DEM}$ = 5V, SENSE+ = SENSE- = 0V, no switching                                     |       | 1600 |          | μΑ   |

| V <sub>IN</sub> DEM current                         | IQ_DEM                 | EXTBIAS = 0V, $V_{CCM/DEM}$ = 0.6V, $V_{FB}$ = 0.84V, SENSE+ = SENSE- = 12V, no switching                                  |       | 500  |          | μΑ   |

| V <sub>IN</sub> shutdown current                    | Ishdn                  | V <sub>EN</sub> = 0V                                                                                                       |       | 5    | 15       | μΑ   |

| VCC Regulator                                       |                        |                                                                                                                            |       |      |          |      |

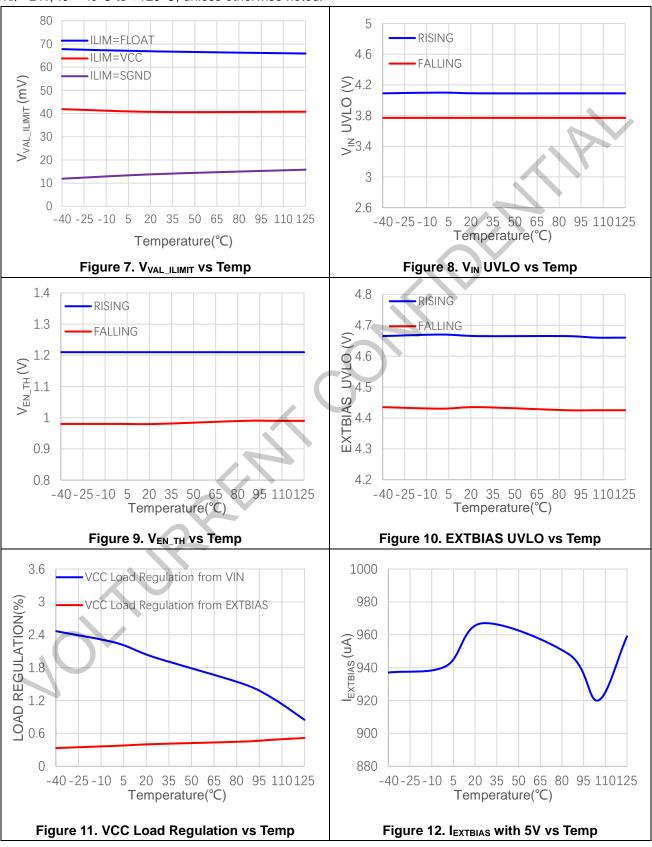

| VCC regulator output voltage from V <sub>IN</sub>   | VCC <sub>VIN</sub>     | $V_{IN} > 6V$ , $I_{LOAD} = 0$ to $50mA$                                                                                   | 4.75  | 5    | 5.25     | V    |

| VCC regulator load regulation from V <sub>IN</sub>  |                        | I <sub>LOAD</sub> = 0 to 50mA, EXTBIAS floating or connected to SGND                                                       |       | 2    | 5        | %    |

| VCC regulator output voltage from EXTBIAS           | VCCextbias             | EXTBIAS > 6V                                                                                                               | 4.75  | 5    | 5.25     | V    |

| VCC regulator load regulation from EXTBIAS          |                        | I <sub>LOAD</sub> = 0 to 50mA,<br>EXTBIAS = 12V                                                                            |       | 1    | 3        | %    |

| EXTBIAS UVLO threshold (rising)                     | EXTBIAS_               |                                                                                                                            | 4.3   | 4.68 | 4.92     | V    |

| EXTBIAS UVLO threshold (falling)                    | EXTBIAS_<br>FALLING    |                                                                                                                            | 4.05  | 4.42 | 4.75     | V    |

| EXTBIAS threshold hysteresis                        | EXTBIAS_               |                                                                                                                            |       | 258  | 278      | mV   |

| EVERIAS cumply current                              | In                     | $V_{DEM} = 5V$ , $V_{FB} = 0.84V$ , $SENSE+ = SENSE- = 12V$ , $EXTBIAS = 12V$ , no switching                               |       | 960  |          | μΑ   |

| EXTBIAS supply current                              | IEXTBIAS               | $V_{\text{DEM}} = 0.6 \text{V}, V_{\text{FB}} = 0.84 \text{V},$<br>SENSE+ = SENSE- = 12 V,<br>EXTBIAS = 12 V, no switching |       | 500  |          | μA   |

| Feedback (FB)                                       |                        |                                                                                                                            |       |      |          |      |

| Feedback voltage                                    | $V_{FB}$               | 4V < V <sub>IN</sub> < 60V                                                                                                 | 0.788 | 0.8  | 0.812    | V    |

| Parameter                               | Symbol                   | Condition                                      | Min  | Тур  | Max  | Unit |  |

|-----------------------------------------|--------------------------|------------------------------------------------|------|------|------|------|--|

| Feedback current                        | I <sub>FB</sub>          | $V_{FB} = 0.8V$                                |      | 10   |      | nA   |  |

| Enable (EN/SYNC)                        |                          |                                                |      |      |      |      |  |

| Enable threshold (rising)               | V <sub>EN_RISING</sub>   |                                                |      | 1.2  | 1.25 | V    |  |

| Enable threshold (falling)              | V <sub>EN_FALLING</sub>  |                                                |      | 1.08 |      | V    |  |

| Enable threshold hysteresis             | V <sub>EN_TH</sub>       |                                                |      | 120  |      | mV   |  |

| Enable input current                    | I <sub>EN</sub>          | V <sub>EN</sub> = 2V                           |      | 1    | 2    | μΑ   |  |

| Enable turn-off delay                   | T <sub>OFF</sub>         |                                                | 18   | 42   | 72   | μs   |  |

| Oscillator and Sync                     |                          |                                                |      |      |      |      |  |

| Operating frequency                     | Fsw                      | $R_{FREQ} = 90 \text{ k}\Omega$                |      | 500  |      | kHz  |  |

| Foldback operating frequency            | Fsw_foldback             | V <sub>FB</sub> = 0.1V                         |      | 50%  |      | Fsw  |  |

| Maximum frequency                       | Fswн                     |                                                | 1000 |      |      | kHz  |  |

| Minimum frequency                       | F <sub>SWL</sub>         |                                                |      |      | 100  | kHz  |  |

| EN/SYNC frequency range                 | Fsync                    |                                                | 100  |      | 1000 | kHz  |  |

| EN/SYNC voltage rising threshold        | Vsync_rising             |                                                | 2    |      |      | V    |  |

| EN/SYNC voltage falling threshold       | Vsync_falling            |                                                |      |      | 0.35 | V    |  |

| Current Sense                           |                          | X                                              |      |      |      |      |  |

| Current sense common mode voltage range | Vsense+/-                |                                                | 0    |      | 65   | V    |  |

|                                         | Vilimit                  | ILIM = SGND, V <sub>SENSE+</sub> = 12V         | 14   | 24   | 34   |      |  |

| Current limit sense voltage             |                          | ILIM = VCC, V <sub>SENSE+</sub> = 12V          | 39   | 49   | 59   | mV   |  |

|                                         |                          | ILIM = FLOAT, V <sub>SENSE+</sub> = 12V        | 64   | 74   | 84   |      |  |

| _                                       |                          | ILIM = SGND, V <sub>SENSE+</sub> = 12V         |      | 8    |      |      |  |

| Reverse current limit sense voltage     | V <sub>REV_ILIMIT</sub>  | ILIM = VCC, V <sub>SENSE+</sub> = 12V          |      | 16   |      | mV   |  |

| voltage                                 |                          | ILIM = FLOAT, V <sub>SENSE+</sub> = 12V        |      | 25   |      |      |  |

|                                         |                          | ILIM = SGND, V <sub>SENSE+</sub> = 12V         |      | 14.5 |      |      |  |

| Valley current limit                    | V <sub>VAL_</sub> ILIMIT | ILIM = VCC, V <sub>SENSE+</sub> = 12V          |      | 41.5 |      | mV   |  |

|                                         |                          | ILIM = FLOAT, V <sub>SENSE+</sub> = 12V        |      | 66.5 |      |      |  |

|                                         |                          | Vsense+ = Vsense- = 12V                        |      |      | 1    | uA   |  |

| lamint arrayant of access               | I <sub>SENSE+</sub>      | VSENSE+ = VSENSE- = 1V                         |      |      | 1    |      |  |

| Input current of sensor                 | 1                        | Vsense+ = Vsense- = 12V                        | 240  | 270  | 300  |      |  |

|                                         | Isense-                  | V <sub>SENSE+</sub> = V <sub>SENSE-</sub> = 1V |      |      | 1    | uA   |  |

| Soft Start (SS)                         |                          |                                                |      |      |      |      |  |

| Soft-start source current               | Iss                      | SS = 0.5V                                      | 2    | 4    | 6    | μA   |  |

| Error Amplifier (EA)                    |                          |                                                | •    |      | •    | -    |  |

| Parameter                | Symbol                 | Condition                 | Min  | Тур  | Max  | Unit            |  |  |  |

|--------------------------|------------------------|---------------------------|------|------|------|-----------------|--|--|--|

| Error amp                | Gм                     | $\Delta V = 5mV$          | 420  | 550  | 720  | 0               |  |  |  |

| transconductance         | <b>G</b> M             | ΔV = SIIIV                | 420  | 550  | 720  | μS              |  |  |  |

| Error amp open loop DC   | Ao                     |                           | 70   | 75   | 82   | dB              |  |  |  |

| gain                     | 7.0                    |                           |      | . 0  | 02   | <u> </u>        |  |  |  |

| Error amp sink/source    | I <sub>EA</sub>        | FB = 0.7/0.9V             |      | ±50  |      | μA              |  |  |  |

| current                  |                        |                           |      |      |      | ·               |  |  |  |

| Protection               | T                      | Г                         |      | Γ    |      |                 |  |  |  |

| Over-voltage threshold   | Vov                    |                           | 110% | 116% | 120% | V <sub>FB</sub> |  |  |  |

| Over-voltage hysteresis  | V <sub>OV_HYS</sub>    |                           |      | 3%   |      | V <sub>FB</sub> |  |  |  |

| Thermal shutdown         |                        |                           |      | 170  |      | °C              |  |  |  |

| Thermal shutdown         |                        |                           |      | 20   |      | °C              |  |  |  |

| hysteresis               |                        |                           |      |      |      |                 |  |  |  |

| Gate Driver              | T                      |                           |      | ı    | T    |                 |  |  |  |

| TG pull-up resistor      | RTG_PULLUP             |                           |      | 2    |      | Ω               |  |  |  |

| TG pull-down resistor    | RTG_PULLDN             |                           |      | 1    |      | Ω               |  |  |  |

| BG pull-up resistor      | R <sub>BG_PULLUP</sub> |                           |      | 2    |      | Ω               |  |  |  |

| BG pull-down resistor    | RBG_PULLDN             |                           |      | 1    |      | Ω               |  |  |  |

| Dead time                | T <sub>DEAD</sub>      |                           |      | 20   |      | ns              |  |  |  |

| TG maximum duty cycle    | D <sub>MAX</sub>       | V <sub>FB</sub> = 0.7V    | 98   | 99.3 |      | %               |  |  |  |

| TG minimum on time       | Ton_min_tg             |                           |      | 170  |      | ns              |  |  |  |

| BG minimum on time       | T <sub>ON_MIN_BG</sub> |                           |      | 145  |      | ns              |  |  |  |

| Power Good (PG)          |                        | ,                         | •    |      |      |                 |  |  |  |

| Power good low           | V <sub>PG_LOW</sub>    | I <sub>LOAD</sub> = 4mA   |      | 0.2  | 0.3  | V               |  |  |  |

| DO vision with march and | DC.                    | Vout rising               |      | 90%  |      | V <sub>FB</sub> |  |  |  |

| PG rising threshold      | PGvth_rsing            | V <sub>OUT</sub> falling  |      | 110% |      | V <sub>FB</sub> |  |  |  |

| DO CHI HI LA             | D0                     | V <sub>OUT</sub> falling  |      | 88%  |      | V <sub>FB</sub> |  |  |  |

| PG falling threshold     | PGvth_falling          | V <sub>OUT</sub> rising   |      | 112% |      | $V_{FB}$        |  |  |  |

| PG threshold hysteresis  | PGvth_hys              |                           |      | 2%   |      | V <sub>FB</sub> |  |  |  |

| Power good leakage       | I <sub>PG_LK</sub>     | PG = 5V                   |      |      | 2    | μA              |  |  |  |

| 10                       |                        | Rising                    |      | 70   |      |                 |  |  |  |

| Power good delay         | T <sub>PG_DELAY</sub>  | Falling                   |      | 55   |      | μs              |  |  |  |

| DEM Mode/CCM             |                        |                           |      |      |      |                 |  |  |  |

| DEM mode output current  | I <sub>DEM</sub>       | R <sub>FREQ</sub> = 90 kΩ |      | 6.5  |      | μΑ              |  |  |  |

| CCM required DEM         | 1/                     |                           | _    |      |      | \/              |  |  |  |

| threshold voltage        | V <sub>ССМ_ТН</sub>    |                           | 3    |      |      | V               |  |  |  |

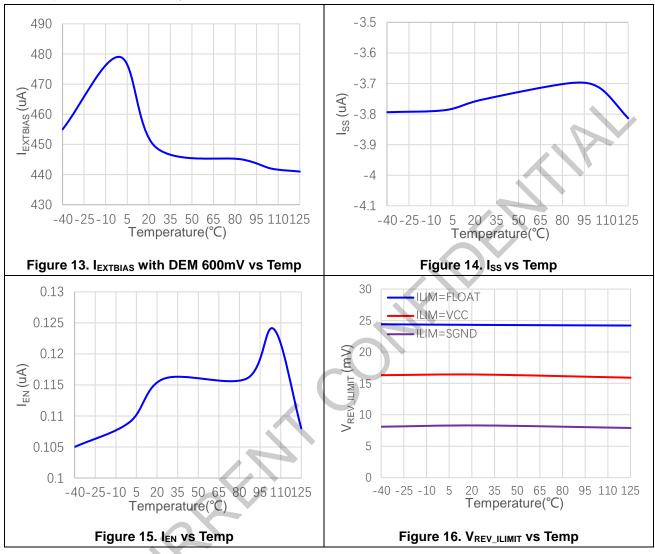

$V_{IN} = 24V$ ,  $T_J = -40$ °C to +125°C, unless otherwise noted.

$V_{IN} = 24V$ ,  $T_{J} = -40$ °C to +125°C, unless otherwise noted.

V<sub>IN</sub> = 24V, T<sub>J</sub> = -40°C to +125°C, unless otherwise noted

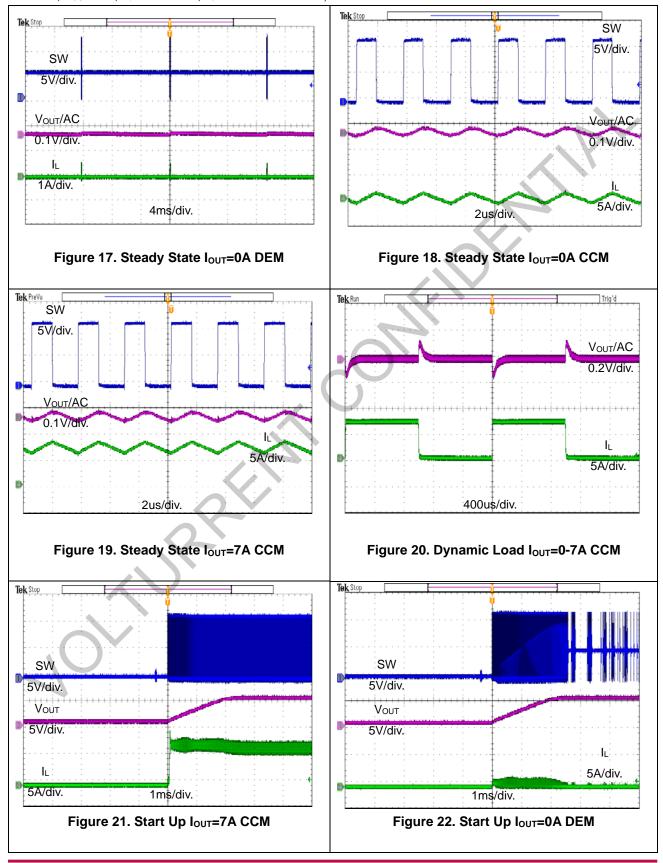

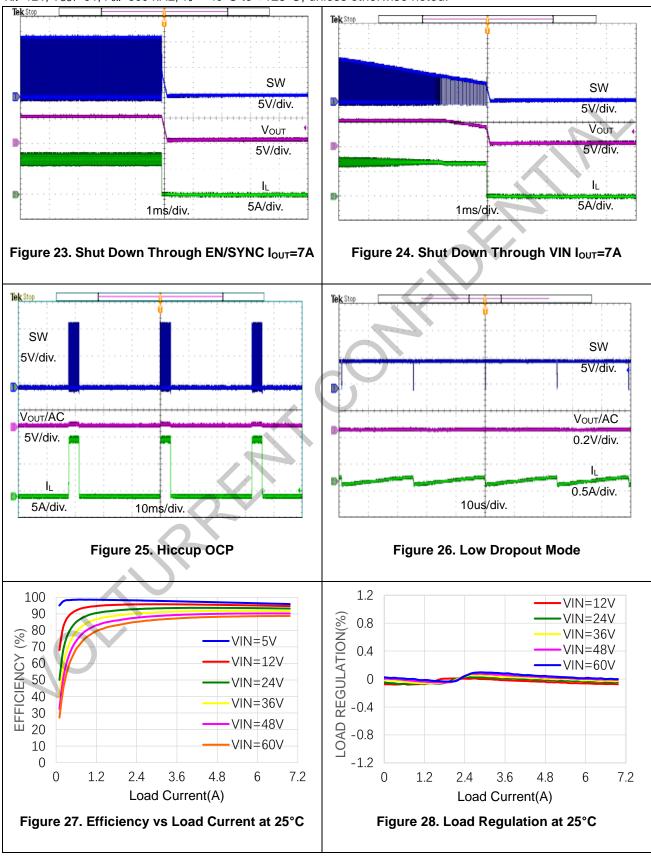

V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 5V, F<sub>SW</sub> = 300 kHz, T<sub>J</sub> = -40°C to +125°C, unless otherwise noted.

$V_{IN}=12V$ ,  $V_{OUT}=5V$ ,  $F_{sw}=300$  kHz,  $T_{J}=-40$ °C to +125°C, unless otherwise noted.

#### **FUNCTION DESCRIPTION**

#### **General Description**

The VE8600 is a high-performance, step-down, synchronous, DC/DC controller IC with a wide input voltage range. It implements current mode control and an internal slope compensation to avoid the subharmonic oscillation.

#### **Diode Emulation Mode**

The VE8600 offers diode emulation mode (DEM) functionality to optimize efficiency during light load. DEM is enabled when CCM/DEM is at a low level by connecting an appropriate resistor (RCCM/DEM) to SGND. The recommended value for RCCM/DEM is

The value less than 0.5R<sub>FREQ</sub> is not allowed but the value higher than 1.5R<sub>FREQ</sub> and less than 3R<sub>FREQ</sub> is allowed. The higher value of R<sub>CCM/DEM</sub> increases output voltage ripple but reduces the power loss during light load.

#### **Gate Driver**

The low-side gate driver is supplied from VCC. The high-side gate driver is supplied from BST. A boot capacitor connected from the BST to the VCC provides power to the high-side MOSFET driver. This floating driver has its own under-voltage lockout (UVLO) protection. This UVLO's rising threshold is 3.6V with a hysteresis of 100mV. If the BST voltage is lower than the bootstrap UVLO, the VE8600 enters boot refresh mode to ensure that the BST capacitor is high enough to drive the HS-FET.

## **Error Amplifier**

The error amplifier compares  $V_{FB}$  with the internal 0.8V reference and outputs a current proportional to the difference between the two input voltages. This output current is then used to charge or discharge the external compensation network to form  $V_{COMP}$ , which is used to control the inductor current. Adjusting the compensation network from COMP to SGND optimizes the control loop for good stability or fast transient response.

#### **Current Limit Function**

There are three fixed current limit options: 23mV, when ILIM is connected to SGND; 48mV, when ILIM is connected to VCC; and 74mV, when ILIM is floating.

When the peak value of the inductor current exceeds the set current-limit threshold, the output voltage begins dropping until FB is 37.5% below the reference. The VE8600 enters hiccup mode to restart the part periodically. All switchers are turned off for 28ms before a re-start up is issued. The frequency is lowered when FB is below 0.4V. This protection mode is especially useful when the output is dead shorted to ground. The average short circuit current is reduced greatly to alleviate thermal issues. The VE8600 exits hiccup mode once the overcurrent condition is removed.

The VE8600 works on peak valley current limit mode and the hiccup mode is disabled when the voltage on the ILIM is between 0.64V and 1.5V before soft start. The current limit threshold can be calculated by Equation(1):

$$I_{LIM} = \frac{V_{ILIM} - 0.64}{10 \times R_{S}}$$

(1)

#### **Low Dropout Mode**

In low dropout mode, the VE8600 is designed to operate in low frequency mode as long as the off time is minoff time, improving dropout, increasing the effective duty cycle of the switching regulator. Low dropout operation makes the VE8600 suitable for automotive cold-crank applications.

#### **Power Good**

The VE8600 includes an open-drain power good output that indicates whether the regulator's output is within  $\pm 10\%$  of its nominal value. When the output voltage falls outside of this range, the PG output is pulled low. PG should be connected to a voltage source no more than 5V through a resistor (e.g.:  $100k\Omega$ ).

#### Soft Start (SS)

Soft start (SS) is implemented to prevent the converter output voltage from overshooting during start-up. When the chip starts up, the internal circuitry generates a soft-start voltage that ramps up from 0V to 2.8V. When it is lower than REF, SS overrides REF, so the error amplifier uses SS as the reference. When SS is higher than REF, REF regains control.

An external capacitor connected from SS to SGND is charged from an internal  $4\mu A$  current source, producing a ramped voltage. The soft- start time ( $T_{SS}$ ) is set by the external SS capacitor and can be calculated by Equation (2):

$$T_{SS}(ms) = \frac{C_{SS}(nF) \times V_{REF}(V)}{I_{SS}(uA)}$$

(2)

Where  $C_{SS}$  is the external SS capacitor,  $V_{REF}$  is the internal reference voltage (0.8V), and  $I_{SS}$  is the 4 $\mu$ A SS charge current. There is no internal SS capacitor. SS is reset when a fault protection other than OVP or peak valley current limit occurs.

## **Programmable Switching Frequency**

The VE8600's frequency can be programmed from 100kHz to 1000kHz with a resistor from FREQ to SGND. The Value of  $R_{FREQ}$  can be calculated with Equation (3):

$$R_{FREQ}(K\Omega) = \frac{1000}{0.0202 \times F_{SW}(KHz)} - 9$$

(3)

#### **OVP**

The output over-voltage is monitored by  $V_{FB}$ . If  $V_{FB}$  is typically 16% higher than the reference, the VE8600 enters discharge mode. The HS-FET turn off, and the LS-FET turns on. The LS-FET remains on until the reverse current limit is triggered. The LS-FET then turns off, and the inductor current increases to 0. The LS-FET is turned on again after ZCD is triggered. The VE8600 works in discharge mode until the over-voltage condition is cleared.

#### **EN/SYNC**

The VE8600 has a dedicated enable (EN/SYNC) control that uses a bandgap- generated precision threshold of 1.2V. By pulling EN/SYNC high or low, the IC can be enabled or disabled. To disable the part, EN/SYNC must be pulled low for at least 42µs. The device can be synchronized to an external clock ranging from 100kHz up to 1000kHz through EN/SYNC. The internal clock rising edge is synchronized to the external clock rising edge. The pulse width (both high and low) of the external clock signal should be no less than 100ns. The frequency applied on EN/SYNC pin of external clock must be higher than the frequency set by the FREQ pin.

#### **SYNCO Function**

The SYNCO pin outputs a default 180° phase shifted clock when VE8600 works in CCM. This function allows two devices operate in same frequency but 180° out of phase to reduce the total input current ripple. The SYCNO outputs a high level when VE8600 works on skip mode. The SYNCO pin outputs a default 180° phase shifted clock when it is synchronized by external clock.

#### **Dithering Function**

If VE8600 is set to CCM. It works on dithering mode when the SYNCO pin is shorted to GND before start up.

#### **UVLO**

Under-voltage lockout (UVLO) is implemented to protect the chip from operating at an insufficient input supply voltage. The VE8600 UVLO rising threshold is about 4.1V, while its falling threshold is a consistent 3.8V.

#### **Thermal Protection**

Thermal protection prevents damage to the IC from excessive temperature. The die temperature is monitored internally until the thermal limit is reached. When the silicon die temperature is higher than 170°C, the entire chip shuts down. When the temperature is lower than its lower threshold (typically 150°C), the chip is enabled again.

#### Start-Up and Shutdown

If both  $V_{IN}$  and EN/SYNC are higher than their respective thresholds, the chip starts up. The reference block starts first, generating stable reference voltages and currents. The internal regulator is then enabled. The regulator provides a stable supply for the remaining circuitry. Three events can shut down the chip: EN low,  $V_{IN}$  low, and thermal shutdown. During the shutdown procedure, the signal path is blocked first to avoid any fault triggering.  $V_{COMP}$  and the internal supply rail are then pulled down.

## Pre-Bias Start-Up

If SS is less than FB at start-up, and the output has a pre-bias voltage, neither TG nor BG is turned on until SS is greater than FB.

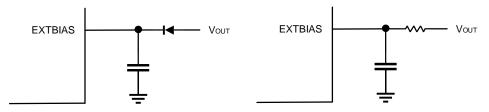

## **VCC Regulator Connection**

VCC can be powered from both VIN and EXTBIAS. If connecting EXTBIAS to an external power supply to improve the overall efficiency, EXTBIAS should be higher than 5V but less than 24V. If  $V_{OUT}$  is higher than 4.7V but less than 24V, EXTBIAS can be connected to  $V_{OUT}$  with a resistor or diode. The recommend value of this resistor is  $10\Omega$ .

Figure 29. VCC Regulator Connection

#### **APPLICATION**

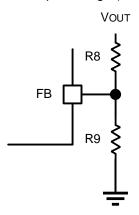

#### Setting the output voltage

The external resistor divider is used to set the output voltage (see Figure 30.).

Figure 30. Setting the Output Voltage

If R8 is known, then R9 can be calculated with Equation (4):

R9 = R8

$$\div (\frac{V_{OUT}}{0.8V} - 1)$$

(4)

#### **Setting Current Limit**

The VE8600 has three fixed current limit options: 23mV (V<sub>SENSE+</sub> - V<sub>SENSE-</sub>), when ILIM is connected to SGND; 48mV, when ILIM is connected to VCC; and 74mV, when ILIM is floating. Ensure that the application can deliver a full load of current over the full operating temperature range when setting ILIM.

The current sense resistor (R<sub>SENSE</sub>) monitors the inductor current. Its value is chosen based on the current limit threshold. The relationship between the peak inductor current (I<sub>PK</sub>) and R<sub>SENSE</sub> can be calculated with Equation (5):

$$R_{SENSE} = \frac{V_{ILIMIT}}{I_{PK}}$$

(5)

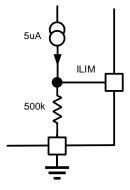

The VE8600 works on peak valley current limit mode and the hiccup mode is disabled when the voltage on the ILIM is between 0.64V and 1.5V before soft start. The current limit threshold can be calculated by Equation (1). The VE8600 integrates a 5uA current source and a  $500k\Omega$  resistor. The Voltage on the ILIM pin is 2.5V when this pin is floating.

Figure 31. ILIM Internal Circuit

#### Slope compensation

An internal slope compensation is designed to avoid the subharmonic issue. The value of this slope is 400mV when the duty cycle is maximum. To avoid the subharmonic issue the inductor L can be calculated with Equation (6):

$$L > \frac{V_{OUT} \times 12 \times R_{SENSE}}{0.8 \times Fsw}$$

(6)

where Fsw is the switching frequency.

## **BST Charge Diode and Resistor Selection**

The recommended external BST diode is a Schottky diode. The recommended BST capacitor value is 0.1µF to 1µF and it must be less than 1/10 Cvcc. A resistor in series with the BST capacitor (RBST) can reduce the SW rising rate and voltage spikes. This helps enhance EMI performance and reduce voltage stress at a high V<sub>IN</sub>. A higher resistance is better for SW spike reduction but compromises efficiency. To make a tradeoff between EMI and efficiency, a  $\leq 20\Omega$  R<sub>BST</sub> is recommended.

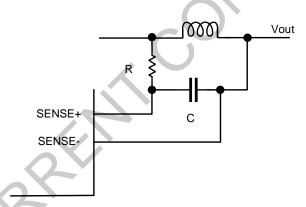

#### DCR sensing

For the applications requiring low cost with low power loss, DCR is used to sense the inductor current rather than using a sense resistor. Shown in Figure 32. is a DCR sensing configuration.

Figure 32. DCR sensing configuration

R and C selection should meet Equation (7) since this indirect current sensing method requires a time constant matching. R is usually selected to be in the range of  $1k\Omega$  to  $10k\Omega$  and C can be calculated with Equation (7):

$$C = \frac{L}{DCR \times R}$$

(7)

### Switching frequency

Switching frequency selection is a trade-off between efficiency and component size. Low switching frequency improves efficiency by reducing MOSFET switching loss. To meet the output ripple and load transient requirements, operation at a low switching frequency requires larger inductance and output capacitance. The switching frequency of the VE8600 is set by a resistor connected from the FREQ pin to GND according to Equation (3). In noise-sensitive applications, the switching frequency should be out of a sensitive frequency band.

#### Selecting the Inductor

An inductor with a DC current rating at least 20% higher than the maximum load current is recommended for most applications. A larger value inductor results in less ripple current and a lower output ripple voltage. However, the larger value inductor has a larger size, higher series resistance, and lower saturation current. Choose the inductor ripple current to be approximately 20%~50% of the maximum load current. The inductance values can be calculated with Equation (8):

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_L \times F_{SW}}$$

(8)

#### **Selecting the Output Capacitor**

The output capacitor is used to hold output voltage and suppress the output voltage ripple. The output voltage ripple can be estimated with Equation (9):

$$V_{\text{RIPPLE}} = \frac{V_{\text{OUT}}}{L \times F_{\text{SW}}} \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \left(R_{\text{ESR}} + \frac{1}{8F_{\text{SW}} \times C_{\text{O}}}\right) \tag{9}$$

#### **Power MOSFET Selection**

Two N-channel MOSFETs must be selected for the controller: one for the high-side switch, and one for the low-side switch. The driver level of the high-side and low-side MOSFETs is 5V, the logic level MOSFET is recommend.

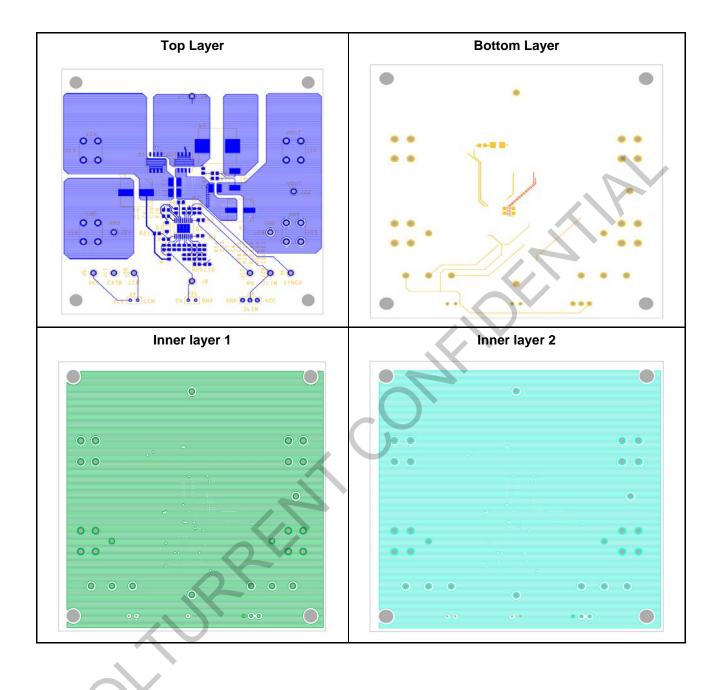

#### **PCB Layout Guidelines**

Efficient PCB layout is critical to achieve good regulation, ripple rejection, transient response, and thermal performance. It is highly recommended to duplicate the EVB layout for optimum performance. If changes are necessary, refer to below figures and follow the guidelines below:

- 1. A four-layer layout is strongly recommended to achieve better thermal performance.

- 2. Place input bypass ceramic capacitors close to VIN pin. Place the MOSFETs as close as possible to the device.

- 3. Place the feedback resistors close to the chip to ensure that the trace which connects to FB is as short as possible. Route SW and BST away from sensitive analog areas such as FB, SENSE+ and SENSE -.

- 4. Use a large ground plane to connect to PGND directly. Add vias near PGND if the bottom layer is a ground plane. Use multiple vias to connect the power planes to the internal layers.

- 5. Ensure the high-current paths at PGND and VIN have short, direct, and wide traces.

- 6. SENSE+ and SENSE are differential pair, make the sense lines run close together, require close parallel and equal length routing. The purpose is to reduce the line drop error.

## **TYPICAL APPLICATION CIRCUITS**

$V_{\text{IN}}$  = 6-60V,  $V_{\text{OUT}}$  = 5V,  $I_{\text{OUT}}$  = 7A application

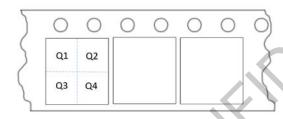

## TAPE AND REEL INFORMATION

| Package    | Carrier<br>Tape | Reel   | Reel<br>Color | Pin1 | Qty/Reel | Reel /<br>Inner<br>Box | Inner<br>Box /<br>Outer<br>Box | Qty/Out<br>Box |

|------------|-----------------|--------|---------------|------|----------|------------------------|--------------------------------|----------------|

| QFN-20     | W=12<br>P=4     | 13inch | Blue          | Q1   | 5000     | 1                      | 8                              | 40000          |

| TSSOP20-EP | W=12<br>P=4     | 13inch | Blue          | Q1   | 4000     | 2                      | 8                              | 64000          |

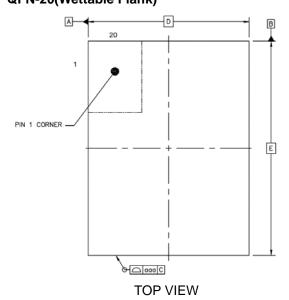

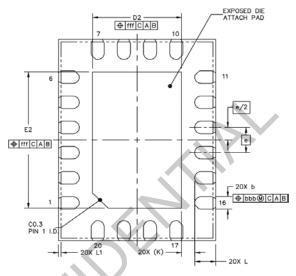

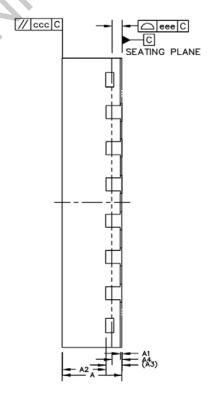

# PACKAGE INFORMATION QFN-20(Wettable Flank)

**BOTTOM VIEW**

|        | Dimensi | ons In Mil | limeters | Dimensions In Inches |          |        |  |

|--------|---------|------------|----------|----------------------|----------|--------|--|

| Symbol | Min.    | Nom.       | Max.     | Min.                 | Nom.     | Max.   |  |

| Α      | 0.70    | 0.75       | 0.8      | 0.028                | 0.030    | 0.031  |  |

| A1     |         | 0.02       | 0.05     |                      | 0.001    | 0.002  |  |

| A2     |         | 0.55       |          |                      | 0.022    | _      |  |

| А3     |         | 0.203REF   |          | -(                   | 0.008REF |        |  |

| A4     | 0.075   |            | 0.18     | 0.003                |          | 0.007  |  |

| b      | 0.2     | 0.25       | 0.3      | 0.008                | 0.010    | 0.012  |  |

| D      |         | 3BSC       |          | C                    | ).118 BS | С      |  |

| E      |         | 4BSC       | <b>V</b> | 0.157 BSC            |          |        |  |

| е      |         | 0.5BSC     |          | 0.020BSC             |          |        |  |

| L      | 0.3     | 0.4        | 0.5      | 0.012                | 0.016    | 0.020  |  |

| D2     | 1.6     | 1.7        | 1.8      | 0.063                | 0.067    | 0.071  |  |

| E2     | 2.6     | 2.7        | 2.8      | 0.102                | 0.106    | 0.110  |  |

| L1     | 0.01    |            | 0.09     | 0.0004               |          | 0.0035 |  |

| К      |         | 0.25REF    |          | 0.                   | .0098 RE | :F     |  |

| aaa    |         | 0.1        |          |                      | 0.004    |        |  |

| bbb    |         | 0.1        |          |                      | 0.004    |        |  |

| ccc    |         | 0.1        |          |                      | 0.004    |        |  |

| eee    |         | 0.08       |          | 0.003                |          |        |  |

| fff    |         | 0.1        |          |                      | 0.004    |        |  |

SIDE VIEW

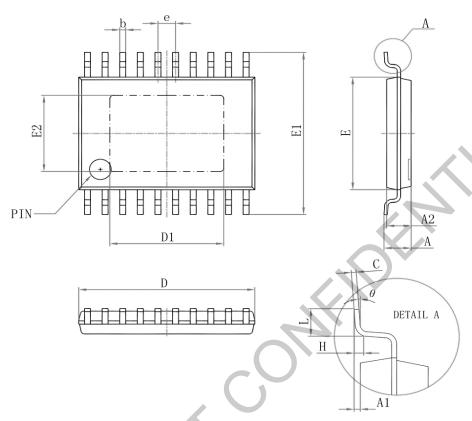

## TSSOP20-EP

| Symbol | Dimensions In Millimeters |      | Dimensions In Inches |       |

|--------|---------------------------|------|----------------------|-------|

|        | Min.                      | Max. | Min.                 | Max.  |

| D      | 6.4                       | 6.6  | 0.252                | 0.259 |

| D1     | 4.1                       | 4.3  | 0.165                | 0.169 |

| E      | 4.3                       | 4.5  | 0.169                | 0.177 |

| b      | 0.19                      | 0.3  | 0.007                | 0.012 |

| С      | 0.09                      | 0.2  | 0.004                | 0.008 |

| E1     | 6.25                      | 6.55 | 0.246                | 0.258 |

| E2     | 2.9                       | 3.1  | 0.114                | 0.122 |

| Α      |                           | 1.1  |                      | 0.043 |

| A2     | 0.8                       | 1.0  | 0.031                | 0.039 |

| A1     | 0.02                      | 0.15 | 0.001                | 0.006 |

| е      | 0.65(BSC)                 |      | 0.026(BSC)           |       |

| L      | 0.5                       | 0.7  | 0.02                 | 0.028 |

| Н      | 0.25(TYP)                 |      | 0.01(TYP)            |       |

| θ      | 1°                        | 7°   | 1°                   | 7°    |

#### **REVISION HISTORY**

| Revision | Data       | Description     |

|----------|------------|-----------------|

| 1.0      | 2024-05-06 | Initial Release |

NOTICE: The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating Volturrent products into any application. Volturrent cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Volturrent product. Volturrent will not assume any legal responsibility for any said applications.