**Features**

##

## ±15kV ESD-Protected USB Transceivers in UCSP with USB Detect

### **General Description**

The MAX3344E/MAX3345E USB transceivers convert logic-level signals to USB signals, and USB signals to logic-level signals. An internal 1.5kΩ USB pullup resistor supports full-speed (12Mbps) USB operation. The MAX3344E/MAX3345E provide built-in ±15kV ESD-protection circuitry on the USB I/O pins, D+ and D-, and VCC.

The MAX3344E/MAX3345E operate with logic supply voltages as low as 1.65V, ensuring compatibility with low-voltage ASICs. The suspend mode lowers supply current to less than 40µA. An enumerate function allows devices to logically disconnect while plugged in. The MAX3344E/MAX3345E are fully compliant with USB specification 1.1, and full-speed operation under USB specification 2.0.

The MAX3344E/MAX3345E have a USB detect that monitors the USB bus for insertion and signals this event. The MAX3344E USB\_DET threshold is between 3.6V (min) and 4V (max), while the MAX3345E USB\_DET threshold is between 1V (min) and 2.8V (max).

The MAX3344E/MAX3345E are available in the miniature  $4 \times 4$  UCSP<sup>TM</sup>, as well as the small 16-pin TSSOP, and are specified over the extended temperature range. -40°C to +85°C.

### **Applications**

Cell Phones

PC Peripherals

Information Appliances

**Data Cradles**

**PDAs**

MP3 Players

Digital Cameras

### ♦ ±15kV ESD Protection On D+ and D-

- ♦ Comply with USB Specification 1.1 (Full Speed 2.0)

- **Separate VP and VM Inputs/Outputs**

- ♦ V<sub>L</sub> Down to 1.65V Allows Connection with Low-Voltage ASICs

- ♦ Enumerate Input—Allows USB Connection through Software

- ♦ USB Detect Function

- 3.6V (min) to 4V (max)—MAX3344E 1V (min) to 2.8V (max)-MAX3345E

- ♦ Allow Single-Ended or Differential Logic I/O

- ♦ Internal Linear Regulator Allows Direct Powering from the USB

- ♦ Internal Pullup Resistor for Full-Speed Operation

- **♦ Three-State Outputs**

- ♦ No Power-Supply Sequencing Required

- **♦ Driver Active in Suspend Mode**

- ♦ Available in Miniature Chip-Scale Package

## **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAX3344EEUE   | -40°C to +85°C | 16 TSSOP    |

| MAX3344EEBE-T | -40°C to +85°C | 4 x 4 UCSP  |

| MAX3345EEUE   | -40°C to +85°C | 16 TSSOP    |

| MAX3345EEBE-T | -40°C to +85°C | 4 x 4 UCSP  |

Pin Configurations appear at end of data sheet.

UCSP is a trademark of Maxim Integrated Products, Inc.

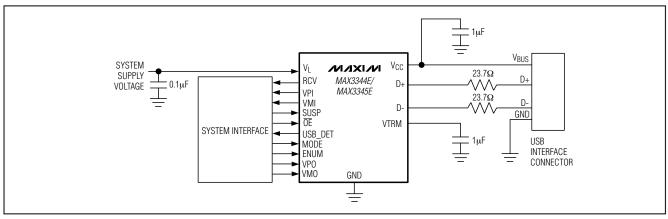

## Typical Operating Circuit

NIXIN

### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages refer to GND, unless otherwis       | se noted.)                   |

|---------------------------------------------------|------------------------------|

| Supply Voltage (V <sub>CC</sub> )                 | 0.3V to +6V                  |

| Output of Internal Regulator (VTRM)               | $-0.3V$ to $(V_{CC} + 0.3V)$ |

| Input Voltage (D+, D-)                            | 0.3V to +6V                  |

| System Supply Voltage (V <sub>L</sub> )           | 0.3V to +6V                  |

| RCV, SUSP, VMO, MODE, VPO, $\overline{OE}$ , VMI, |                              |

| VPI, USB_DET, ENUM                                | 0.3V to $(V_L + 0.3V)$       |

| Short-Circuit Current (D+, D-) to VCC or          |                              |

| GND (Note 1)                                      | Continuous                   |

| Maximum Continuous Current (all other pins)           | ±15mA          |

|-------------------------------------------------------|----------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| 16-Pin TSSOP (derate 9.4mW/°C above +70°C             | )754mW (U16-2) |

| 4 x 4 UCSP (derate 8.2mW/°C above +70°C)              | 659mW (B16-1)  |

| Operating Temperature Range                           | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Bump Temperature (soldering) Reflow                   | +235°C         |

|                                                       |                |

**Note 1:** External 23.7 $\Omega$  resistors connected to D+ and D-.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(VCC = 4V to 5.5V bypassed with 1 $\mu$ F to GND, GND = 0, V $_L$  = 1.65V to 3.6V, ENUM = V $_L$ , T $_A$  = T $_{MIN}$  to T $_{MAX}$ , unless otherwise noted. Typical values are at V $_{CC}$  = 5V, V $_L$  = 2.5V, T $_A$  = +25°C.) (Note 2)

| PARAMETER SYMBO                                         |                      | CONDITIONS                                                                      |                      | TYP | MAX  | UNITS |  |

|---------------------------------------------------------|----------------------|---------------------------------------------------------------------------------|----------------------|-----|------|-------|--|

| SUPPLY INPUTS (VCC, VTRM, V                             | /L)                  |                                                                                 | •                    |     |      | •     |  |

| Regulated Supply Voltage<br>Output                      | V <sub>VTRM</sub>    | Internal regulator                                                              | 3.0                  | 3.3 | 3.6  | V     |  |

| V <sub>CC</sub> Input Range                             | Vcc                  |                                                                                 | 4.0                  |     | 5.5  | V     |  |

| V <sub>L</sub> Input Range                              | VL                   |                                                                                 | 1.65                 |     | 3.60 | V     |  |

| Operating V <sub>CC</sub> Supply Current                | lvcc                 | Full-speed transmitting/receiving at 12Mbps, C <sub>L</sub> = 50pF on D+ and D- |                      |     | 10   | mA    |  |

| Operating V <sub>L</sub> Supply Current I <sub>VL</sub> |                      | Full-speed transmitting/receiving at 12Mbps                                     |                      |     | 8    | mA    |  |

| Full-Speed Idle and SE0 Supply                          | 1                    | Full-speed idle: $V_{D+} > 2.7V$ , $V_{D-} < 0.3V$                              |                      | 340 | 450  |       |  |

| Current                                                 | IVCC(IDLE)           | SE0: V <sub>D+</sub> < 0.3V, V <sub>D-</sub> < 0.3V                             |                      | 390 | 500  | μΑ    |  |

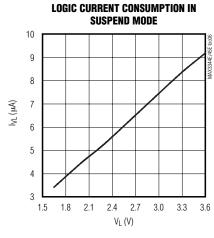

| Static V <sub>L</sub> Supply Current                    | IVL(STATIC)          | Full-speed idle, SE0, or suspend mode                                           |                      |     | 12.5 | μΑ    |  |

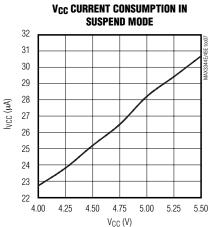

| Suspend Supply Current                                  | Ivcc(susp)           | $SUSP = \overline{OE} = high$                                                   |                      |     | 40   | μΑ    |  |

| Disable-Mode Supply Current                             | IVCC(DIS)            | V <sub>L</sub> = GND or open                                                    |                      |     | 20   | μΑ    |  |

| D+/D- Disable-Mode<br>Load Current                      | I <sub>D_(DIS)</sub> | $V_L = GND \text{ or open}, V_{D} = 0 \text{ or } +5.5V$                        |                      |     | 5    | μΑ    |  |

| Sharing-Mode V <sub>L</sub> Supply<br>Current           | IVL(SHARING)         | V <sub>CC</sub> = GND or open, $\overline{OE}$ = low, SUSP = high               |                      |     | 20   | μΑ    |  |

| D+/D- Sharing-Mode<br>Load Current                      | ID_(SHARING)         | V <sub>CC</sub> = GND or open, V <sub>D</sub> = 0 or +5.5V                      |                      |     | 20   | μΑ    |  |

| LOGIC-SIDE I/O                                          |                      |                                                                                 |                      |     |      |       |  |

| Input High Voltage                                      | VIH                  | SUSP, MODE, ENUM, OE, VMO, VPO                                                  | 2/3 x V <sub>l</sub> | _   |      | V     |  |

| Input Low Voltage                                       | VIL                  | SUSP, MODE, ENUM, $\overline{\text{OE}}$ , VMO, VPO                             |                      |     | 0.4  | V     |  |

| Output-Voltage High                                     | VoH                  | VPI, VMI, RCV, USB_DET; ISOURCE = 2mA                                           | V <sub>L</sub> - 0.4 | +   |      | V     |  |

| Output-Voltage Low                                      | V <sub>OL</sub>      | VPI, VMI, RCV, USB_DET; ISINK = -2mA                                            |                      |     | 0.4  | V     |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 4V \text{ to } 5.5V \text{ bypassed with } 1\mu\text{F to GND, GND} = 0$ ,  $V_L = 1.65V \text{ to } 3.6V, \text{ENUM} = V_L, T_A = T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{CC} = 5V$ ,  $V_L = 2.5V$ ,  $T_A = +25^{\circ}\text{C.}$ ) (Note 2)

| PARAMETER                               | SYMBOL            | CONDITIONS                                                 | MIN   | TYP   | MAX   | UNITS |  |

|-----------------------------------------|-------------------|------------------------------------------------------------|-------|-------|-------|-------|--|

| Input Leakage Current                   |                   | SUSP, MODE, ENUM, $\overline{OE}$ , VMO, VPO = 0 or $V_L$  |       |       | ±1    | μΑ    |  |

| USB-SIDE I/O                            |                   |                                                            |       |       |       |       |  |

| Output-Voltage Low                      | VoL               | $R_L = 1.5k\Omega$ from D+ or D- to 3.6V                   |       |       | 0.3   | V     |  |

| Output-Voltage High                     | Voh               | $R_L = 15k\Omega$ from D+ and D- to GND                    | 2.8   |       | 3.6   | V     |  |

| Input Impedance                         | Z <sub>IN</sub>   | Three-state driver, ENUM = 0, $V_{D_{\perp}}$ = 0 or +3.6V | 1     |       |       | МΩ    |  |

| Single-Ended Input-Voltage High         | VIH               |                                                            | 2.0   |       |       | V     |  |

| Single-Ended Input-Voltage Low          | V <sub>IL</sub>   |                                                            |       |       | 0.8   | V     |  |

| Receiver Single-Ended<br>Hysteresis     | V <sub>H</sub> YS |                                                            |       | 200   |       | mV    |  |

| Differential Input Sensitivity          | V <sub>DIFF</sub> |                                                            | 200   |       |       | mV    |  |

| Input Common-Mode Voltage<br>Range      | V <sub>СМ</sub>   |                                                            | 0.8   |       | 2.5   | V     |  |

| Driver Output Impedance                 | Rout              |                                                            | 4.6   |       | 16.0  | Ω     |  |

| Internal Pullup Resistor                | R <sub>PU</sub>   |                                                            | 1.410 | 1.500 | 1.540 | kΩ    |  |

|                                         | Vusblh1           | MAX3344E                                                   |       |       | 4.0   |       |  |

| USB_DET Threshold                       | Vusbhl1           | MAX3344E                                                   | 3.6   |       |       | V     |  |

| OSB_DET THIESHOLD                       | Vusblh2           | MAX3345E                                                   |       |       | 2.8   | v     |  |

|                                         | VUSBHL2           | MAX3345E                                                   | 1     |       |       |       |  |

| USB_DET Hysteresis                      | Vusbhys           | MAX3344E                                                   |       | 25    |       | mV    |  |

| LINEAR REGULATOR                        |                   |                                                            |       |       |       |       |  |

| External Capacitor                      | Cout              | Compensation of linear regulator                           | 1     |       |       | μF    |  |

| ESD PROTECTION (V <sub>CC</sub> , D+, D | -)                |                                                            |       |       |       |       |  |

| Human Body Model                        |                   |                                                            |       | ±15   |       | kV    |  |

| IEC 1000-4-2 Air-Gap Discharge          |                   |                                                            |       | ±10   |       | kV    |  |

| IEC 1000-4-2 Contact Discharge          |                   |                                                            |       | ±8    |       | kV    |  |

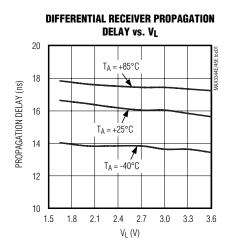

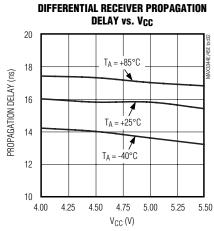

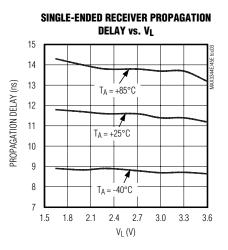

### **TIMING CHARACTERISTICS**

$(V_{CC}=4V\ to\ 5.5V,\ GND=0,\ V_L=1.65V\ to\ 3.6V,\ ENUM=V_L,\ T_A=T_{MIN}\ to\ T_{MAX},\ unless otherwise\ noted.$  Typical values are at  $V_{CC}=5V,\ V_L=2.5V,\ T_A=+25^\circ C.)$  (Figures 2–6) (Note 2)

| PARAMETER                                             | SYMBOL           | CONDITIONS                    | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------|------------------|-------------------------------|-----|-----|-----|-------|

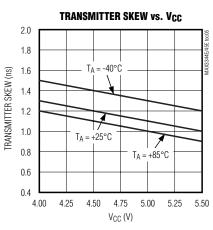

| TRANSMITTER                                           |                  |                               |     |     |     |       |

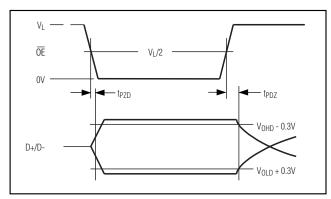

| OE to Transmit Delay Enable Time                      | t <sub>PZD</sub> | Figures 2 and 6c              |     |     | 20  | ns    |

| OE to Driver Three-State Delay<br>Driver Disable Time | t <sub>PDZ</sub> | Figures 2 and 6c              |     |     | 20  | ns    |

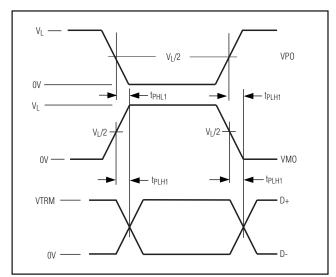

| VPO/VMO to D+/D- Propagation                          | tPLH1(drv)       | MODE = high, Figures 4 and 6b |     | 10  | 18  | 20    |

| Delay                                                 | tPHL1(drv)       | MODE = high, Figures 4 and 6b |     | 10  | 18  | ns    |

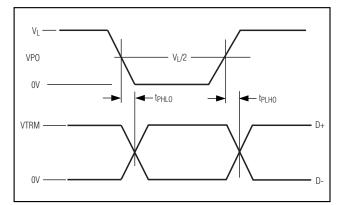

| VPO/VMO D+/D- Propagation                             | tPLH0(drv)       | MODE = low, Figures 3 and 6c  |     | 11  | 20  | 20    |

| Delay                                                 | tPHL0(drv)       | MODE = low, Figures 3 and 6c  |     | 11  | 20  | ns    |

### **TIMING CHARACTERISTICS (continued)**

$(V_{CC}=4V\ to\ 5.5V,\ GND=0,\ V_L=1.65V\ to\ 3.6V,\ ENUM=V_L,\ T_A=T_{MIN}\ to\ T_{MAX},\ unless otherwise\ noted.$  Typical values are at  $V_{CC}=5V,\ V_L=2.5V,\ T_A=+25^\circ C.)$  (Figures 2-6) (Note 2)

| PARAMETER                                 | SYMBOL                           | CONDITIONS                                                                | MIN | TYP | MAX | UNITS |  |  |  |

|-------------------------------------------|----------------------------------|---------------------------------------------------------------------------|-----|-----|-----|-------|--|--|--|

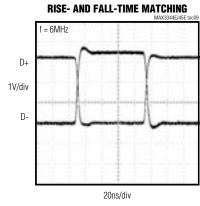

| Rise Time D+/D-                           | t <sub>R1</sub>                  | C <sub>L</sub> = 50pF, 10% to 90% of IV <sub>OH</sub> - V <sub>OL</sub> I | 4   |     | 20  | ns    |  |  |  |

| Fall Time D+/D-                           | t <sub>F1</sub>                  | C <sub>L</sub> = 50pF, 90% to 10% of IV <sub>OH</sub> - V <sub>OL</sub> I | 4   |     | 20  | ns    |  |  |  |

| Rise- and Fall-Time Matching              | t <sub>R1</sub> /t <sub>F1</sub> | (Note 3)                                                                  | 90  |     | 111 | %     |  |  |  |

| Output Signal Crossover                   | VCRS                             | (Note 3)                                                                  | 1.3 |     | 2.0 | V     |  |  |  |

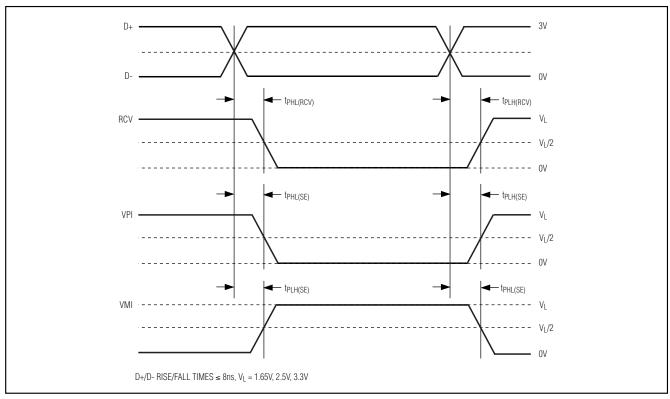

| <b>DIFFERENTIAL RECEIVER</b> (Figures     | 5 and 6a)                        |                                                                           |     |     |     |       |  |  |  |

| D. /D. to DCV Propagation Dalay           | <sup>t</sup> PLH(RCV)            |                                                                           |     |     | 18  | ns    |  |  |  |

| D+/D- to RCV Propagation Delay            | tphl(RCV)                        |                                                                           |     |     | 18  | ns    |  |  |  |

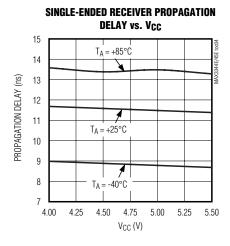

| SINGLE-ENDED RECEIVERS (Figures 5 and 6a) |                                  |                                                                           |     |     |     |       |  |  |  |

| D+/D- to VPI or VMI Propagation           | tPLH(SE)                         |                                                                           |     |     | 18  | ns    |  |  |  |

| Delay                                     | tPHL(SE)                         |                                                                           |     | •   | 18  | ns    |  |  |  |

Note 2: Parameters are 100% production tested at 25°C, limits over temperature are guaranteed by design.

Note 3: Guaranteed by design, not production tested.

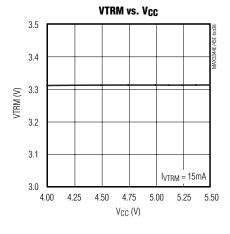

## Typical Operating Characteristics

$(V_{CC} = 5V, V_{I} = 3.3V, T_{A} = +25^{\circ}C, \text{ unless otherwise noted.})$

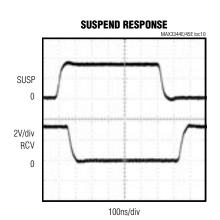

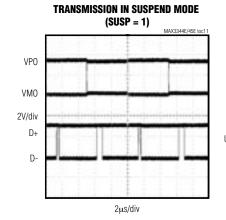

## Typical Operating Characteristics (continued)

$(V_{CC} = 5V, V_L = 3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Pin Description**

| PIN   |      | NAME    | INPUT/           | FUNCTION                                                                                                                                                                                                                                                                                                |

|-------|------|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP | UCSP | NAME    | OUTPUT           | FUNCTION                                                                                                                                                                                                                                                                                                |

| 1     | D2   | RCV     | Output           | Receiver Output. Single-ended CMOS output. RCV responds to the differential input on D+ and D                                                                                                                                                                                                           |

| 2     | D1   | VPO     | Input            | Logic-Level Data Input. VPO is level translated to D+.                                                                                                                                                                                                                                                  |

| 3     | C2   | MODE    | Input            | Mode-Control Input. Selects differential (mode 1) or single-ended (mode 0) input for the system side when converting logic-level signals to USB level signals. Force MODE high to select mode 1. Force MODE low to select mode 0.                                                                       |

| 4     | C1   | VMO     | Input            | Logic-Level Data Input. VMO is level translated to D                                                                                                                                                                                                                                                    |

| 5     | B1   | ŌĒ      | Input            | Output Enable. Drive $\overline{OE}$ low to enable data transmission on D+ and D Drive $\overline{OE}$ high to disable data transmission or to receive data.                                                                                                                                            |

| 6     | B2   | SUSP    | Input            | Suspend Input. Drive SUSP low for normal operation. Drive SUSP high for low-power state. In low-power state, RCV is low and VPI/VMI are active.                                                                                                                                                         |

| 7     | A1   | VPI     | Output           | Logic-Level Data Output. VPI is the level-translated value of D+.                                                                                                                                                                                                                                       |

| 8     | A2   | VMI     | Output           | Logic-Level Data Output. VMI is the level-translated value of D                                                                                                                                                                                                                                         |

| 9     | В3   | ENUM    | Input            | Enumerate. Drive ENUM high to connect the internal $1.5k\Omega$ resistor from D+ to $3.3V$ . Drive ENUM low to disconnect the internal $1.5k\Omega$ resistor.                                                                                                                                           |

| 10    | А3   | Vcc     | Power            | USB-Side Power-Supply Input. Connect $V_{CC}$ to the incoming USB power supply. Bypass $V_{CC}$ to GND with a $1\mu F$ ceramic capacitor.                                                                                                                                                               |

| 11    | A4   | GND     | Power            | Ground                                                                                                                                                                                                                                                                                                  |

| 12    | B4   | D-      | Input/<br>Output | Negative USB Differential Data Input/Output. Connect to the USB's D- signal through a $23.7\Omega$ ±1% resistor.                                                                                                                                                                                        |

| 13    | C4   | D+      | Input/<br>Output | Positive USB Differential Data Input/Output. Connect to the USB's D+ signal through a $23.7\Omega$ ±1% resistor.                                                                                                                                                                                        |

| 14    | D4   | VTRM    | Power            | Regulated Output Voltage. VTRM provides a 3.3V output derived from $V_{CC}$ . Bypass VTRM to GND with a $1\mu F$ (min) low-ESR capacitor, such as ceramic or plastic film types.                                                                                                                        |

| 15    | D3   | VL      | Power            | System-Side Power-Supply Input. Connect to the system's logic-level power supply, 1.65V to 3.6V.                                                                                                                                                                                                        |

| 16    | С3   | USB_DET | Output           | USB Detector Output. A high at USB_DET signals to the ASIC that V <sub>CC</sub> is present. A low at USB_DET indicates that V <sub>CC</sub> is not present. The MAX3344E USB_DET threshold is between 3.6V (min) and 4V (max), while the MAX3345E USB_DET threshold is between 1V (min) and 2.8V (max). |

### Detailed Description

The MAX3344E/MAX3345E are bidirectional transceivers that convert single-ended or differential logic-level signals to differential USB signals, and convert differential USB signals to single-ended or differential logic-level signals. The MAX3344E/MAX3345E are operational from V<sub>CC</sub> = 5.5V to V<sub>CC</sub> = 3V (electrical specifications are not guaranteed for V<sub>CC</sub> < 4V). Both devices include an internal  $1.5 \mathrm{k}\Omega$  pullup resistor that connects and disconnects D+ to VTRM (see the Functional Diagram).

The MAX3344E/MAX3345E are tolerant to power sequencing with either VCC > VL or VL > VCC. Additionally,

the USB I/O, D+ and D-, and V<sub>CC</sub> are ESD protected to  $\pm 15$ kV. The MAX3344E/MAX3345E can receive USB power (V<sub>CC</sub>) directly from the USB connection and operate with logic supplies (V<sub>L</sub>) down to 1.65V, while still meeting the USB physical layer specifications. The MAX3344E/MAX3345E support full-speed (12Mbps) USB specification 2.0 operation.

The MAX3344E/MAX3345E have an enumerate feature that functions when power is applied. Driving ENUM low disconnects the internal 1.5k $\Omega$  pullup resistor from D+ enumerating the USB. This is useful if changes in communication protocol are required while power is applied, and while the USB cable is connected.

### **Power-Supply Configurations**

#### Normal Operating Mode

Connect V<sub>L</sub> and V<sub>CC</sub> to system power supplies (Table 1). Connect V<sub>L</sub> to a +1.65V to +3.6V supply. Connect V<sub>CC</sub> to a +4.0V to +5.5V supply. Alternatively, the MAX3344E/MAX3345E can derive power from a single Li+ battery. Connect the battery to V<sub>CC</sub>. V<sub>VTRM</sub> remains above +3.0V for V<sub>CC</sub> as low as +3.1V.

Additionally, the MAX3344E/MAX3345E can derive power from a 3.3V  $\pm 10\%$  voltage regulator. Connect V<sub>CC</sub> and VTRM to an external  $\pm 3.3$ V voltage regulator.

#### Disable Mode

Connect  $V_{CC}$  to a system power supply and leave  $V_L$  unconnected or connect to GND. D+ and D- enter a tristate mode and  $V_{CC}$  consumes less than  $20\mu A$  of supply current. D+ and D- withstand external signals up to +5.5V in disable mode (Table 2).

### Sharing Mode

Connect V<sub>L</sub> to a system power supply and leave V<sub>CC</sub> (or V<sub>CC</sub> and VTRM) unconnected or connect to GND. D+ and D- enter a tri-state mode, allowing other circuitry to share the USB D+ and D- lines, and V<sub>L</sub> consumes less than 20µA of supply current. D+ and D- withstand external signals up to +5.5V in sharing mode (Table 2).

#### **Device Control**

D+ and D-

D+ and D- are the USB-side transmitter I/O connections, and are ESD protected to  $\pm 15$ kV using the Human Body Model,  $\pm 10$ kV using IEC 1000-4-2 Air-Gap Discharge, and  $\pm 8$ kV using IEC 1000-4-2 Contact Discharge, making the MAX3344E/MAX3345E ideal for applications where a robust transmitter is required. A 23.7 $\Omega$  resistor is required on D+ and D- for normal operation (see the *External Resistors* section).

#### **ENUM**

USB specification 2.0 requires a 1.5k $\Omega$  pullup resistor on D+ for full-speed (12Mbps) operation. Controlled by enumerate (ENUM), the MAX3344E/MAX3345E provide this internal 1.5k $\Omega$  resistor. Drive ENUM high to connect the pullup resistor from D+ to VTRM. Drive ENUM low to disconnect the pullup resistor from D+ to VTRM.

### VPO/VMO, VPI/VMI, and OE

The MAX3344E/MAX3345E system-side inputs are VPO and VMO. Data comes into the MAX3344E/MAX3345E through VPO and VMO. VPO and VMO operate either differentially with VPO as the positive terminal and VMO as the negative terminal, or single ended with VPO as the data input (see the *MODE* section).

**Table 1. Power-Supply Configurations**

| V <sub>CC</sub> (V) | VTRM (V)           | V <sub>L</sub> (V) | CONFIGURATION            | NOTES   |

|---------------------|--------------------|--------------------|--------------------------|---------|

| +4.0 to +5.5        | +3.3 Output        | +1.65 to +3.6      | Normal mode              | _       |

| +3.1 to +4.5        | +3.3 Output        | +1.65 to +3.6      | Battery supply           | _       |

| +3.0 to +3.6        | +3.0 to +3.6 Input | +1.65 to +3.6      | Voltage regulator supply | _       |

| GND or floating     | Output             | +1.65 to +3.6      | Sharing mode             | Table 2 |

| +3.0 to +5.5        | Output             | GND or floating    | Disable mode             | Table 2 |

Table 2. Disable-Mode and Sharing-Mode Configurations

| INPUTS/OUTPUTS        | DISABLE MODE                                                                                                  | SHARING MODE                                                                                                   |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| V <sub>CC</sub> /VTRM | <ul> <li>+5V input/+3.3V output</li> <li>+3.3V input/+3.3V input</li> <li>+3.7V input/+3.3V output</li> </ul> | <ul> <li>Floating or connected to GND</li> <li>&lt; +3.6V (MAX3344E)</li> <li>&lt; +1.0V (MAX3345E)</li> </ul> |  |  |

| VL                    | Floating or connected to GND                                                                                  | +1.65V to +3.6V input                                                                                          |  |  |

| D+ and D-             | High impedance                                                                                                | High impedance                                                                                                 |  |  |

| VDI and VMI           | Invalid*                                                                                                      | High impedance for $\overline{OE}$ = Low                                                                       |  |  |

| VPI and VMI           | invalid                                                                                                       | High for $\overline{OE}$ = High                                                                                |  |  |

| RCV                   | Invalid*                                                                                                      | Undefined**                                                                                                    |  |  |

| SPEED, SUSP, OE, ENUM | High impedance                                                                                                | pedance High impedance                                                                                         |  |  |

<sup>\*</sup>High Impedance or low.

<sup>\*\*</sup>High or low.

The MAX3344E/MAX3345E system-side outputs are VPI, VMI, and RCV. The MAX3344E/MAX3345E send data through VPI, VMI, and RCV. VPI and VMI are outputs to the single-ended receivers and RCV is the output of the differential receiver.

Output enable  $(\overline{OE})$  controls data transmission. Drive  $\overline{OE}$  low to enable data transmission on D+ and D-. Drive  $\overline{OE}$  high to disable data transmission or receive data.

#### MODE

MODE is a control input that selects whether differential or single-ended logic signals are recognized by the system side of the MAX3344E/MAX3345E. Drive MODE high to select differential mode with VPO as the positive terminal and VMO as the negative terminal. Drive MODE low to select single-ended mode with VPO as the data input (Table 3).

#### VTRM

VTRM is the 3.3V output of the internal linear voltage regulator. VTRM powers the internal circuitry of the USB side of the MAX3344E/MAX3345E. Connect a 1 $\mu$ F (min) low-ESR ceramic or plastic capacitor from VTRM to GND, as close to VTRM as possible. Do not use VTRM to power external circuitry.

#### Vcc

Bypass V<sub>CC</sub> to GND with a 1 $\mu$ F ceramic capacitor as close to the device as possible. If V<sub>CC</sub> drops below the USB detect threshold, supply current drops below 20 $\mu$ A avoiding excessive V<sub>CC</sub> current consumption, and D+/D- enter a high-impedance state allowing other devices to drive the lines.

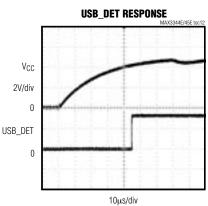

### **USB Detect**

USB detect output (USB\_DET) signals that V<sub>CC</sub> is present. A high at USB\_DET indicates that V<sub>CC</sub> is present, while a low at USB\_DET indicates that V<sub>CC</sub> is not present. The MAX3344E USB\_DET threshold is between 3.6V (min) and 4V (max), while the MAX3345E USB\_DET threshold is between 1V (min) and 2.8V (max).

### SUSP

Suspend (SUSP) is a control input. Force SUSP high to place the MAX3344E/MAX3345E in a low-power state. In this state, the quiescent supply current into V<sub>CC</sub> is less than 40µA and RCV goes low.

In suspend mode, VPI and VMI remain active as receive outputs and VTRM stays on. The MAX3344E/MAX3345E continue to receive data from the USB, allowing the  $\mu P$  to sense activity on the D+/D- lines and wake up the MAX3344E/MAX3345E.

The MAX3344E/MAX3345E can also transmit data to D+ and D- while in suspend mode. This function is

Figure 1a. Human Body ESD Test Models

Figure 1b. Human Body Model Current Waveform

Figure 1c. IEC 1000-4-2 ESD Test Model

used to signal a remote wake-up by driving a signal on D+ and D- for a period of 1ms to 15ms. In suspend mode, data can only be transmitted with full-speed slope control.

Figure 2. Enable and Disable Timing, Transmitter

Figure 3. Mode 0 Timing

Figure 4. Mode 1 Timing

#### **Data Transfer**

#### Receiving Data from the USB

Data received from the USB are output to VPI/VMI in either of two ways, differentially or single ended. To receive data from the USB, force  $\overline{OE}$  high and SUSP low. Differential data arriving at D+/D- appear as differential logic signals at VPI/VMI, and as a single-ended logic signal at RCV. If both D+ and D- are low, then VPI and VMI are low, signaling a single-ended zero condition on the bus; RCV remains in the last known state (Table 3).

#### Transmitting Data to the USB

The MAX3344E/MAX3345E output data to the USB differentially on D+ and D-. The logic driving signals can be either differential or single ended. For sending differential logic, force MODE high, force  $\overline{OE}$  and SUSP low, and apply data to VPO and VMO. D+ then follows VPO, and D- follows VMO. To send single-ended logic signals, force MODE, SUSP, and  $\overline{OE}$  low, and apply data to VPO/VMO.

### **ESD Protection**

To protect the MAX3344E/MAX3345E against ESD, D+ and D- have extra protection against static electricity to protect the device up to  $\pm 15 \text{kV}$ . The ESD structures withstand high ESD in all states—normal operation, suspend, and powered down. For the 15kV ESD structures to work correctly, a 1 $\mu$ F or greater capacitor must be connected from VTRM to GND.

ESD protection can be tested in various ways; the D+ and D- input/output pins are characterized for protection to the following limits:

- 1) ±15kV using the Human Body Model

- 2) ±8kV using the IEC 1000-4-2 Contact Discharge Method

- 3) ±10kV using the IEC 1000-4-2 Air-Gap Method

#### ESD Test Conditions

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

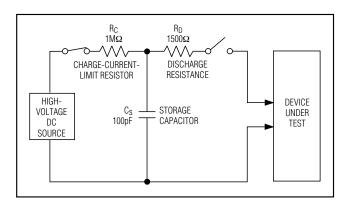

#### Human Body Model

Figure 1a shows the Human Body Model, and Figure 1b shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the test device through a  $1.5 \mathrm{k}\Omega$  resistor.

Table 3a. Truth Table Transmit (SUSP = 0,  $\overline{OE}$  = 0, ENUM = X)

|      | INPUT |     | OUTPUT |    |      |     |     |           |

|------|-------|-----|--------|----|------|-----|-----|-----------|

| MODE | VPO   | VMO | D+     | D- | RCV  | VPI | VMI | RESULT    |

| 0    | 0     | 0   | 0      | 1  | 0    | 0   | 1   | LOGIC 0   |

| 0    | 0     | 1   | 0      | 0  | RCV* | 0   | 0   | SE0       |

| 0    | 1     | 0   | 1      | 0  | 1    | 1   | 0   | LOGIC 1   |

| 0    | 1     | 1   | 0      | 0  | RCV* | 0   | 0   | SE0       |

| 1    | 0     | 0   | 0      | 0  | RCV* | 0   | 0   | SE0       |

| 1    | 0     | 1   | 0      | 1  | 0    | 0   | 1   | LOGIC 0   |

| 1    | 1     | 0   | 1      | 0  | 1    | 1   | 0   | LOGIC 1   |

| 1    | 1     | 1   | 1      | 1  | Х    | 1   | 1   | UNDEFINED |

<sup>\*</sup>RCV denotes the signal level on output RCV just before SE0 state occurs. This level is stable during the SE0 period.

### Table 3b. Truth Table Receive (SUSP = 0, OE = 1, ENUM = X)

| INF | PUT | OUTPUT |     |     |           |  |

|-----|-----|--------|-----|-----|-----------|--|

| D+  | D-  | RCV    | VPI | VMI | RESULT    |  |

| 0   | 0   | RCV*   | 0   | 0   | SE0       |  |

| 0   | 1   | 0      | 0   | 1   | LOGIC 0   |  |

| 1   | 0   | 1      | 1   | 0   | LOGIC 1   |  |

| 1   | 1   | X      | 1   | 1   | UNDEFINED |  |

<sup>\*</sup>RCV denotes the signal level on output RCV just before SE0 state occurs. This level is stable during the SE0 period.

## Table 3c. Truth Table Transmit in Suspend\* (SUSP = 1, $\overline{OE}$ = 0, ENUM = X)

| INPUT |     |     | ОИТРИТ |    |     |     |     |           |  |

|-------|-----|-----|--------|----|-----|-----|-----|-----------|--|

| MODE  | VPO | VMO | D+     | D- | RCV | VPI | VMI | RESULT    |  |

| 0     | 0   | 0   | 0      | 1  | 0   | 0   | 1   | LOGIC 0   |  |

| 0     | 0   | 1   | 0      | 0  | 0   | 0   | 0   | SE0       |  |

| 0     | 1   | 0   | 1      | 0  | 0   | 1   | 0   | LOGIC 1   |  |

| 0     | 1   | 1   | 0      | 0  | 0   | 0   | 0   | SE0       |  |

| 1     | 0   | 0   | 0      | 0  | 0   | 0   | 0   | SE0       |  |

| 1     | 0   | 1   | 0      | 1  | 0   | 0   | 1   | LOGIC 0   |  |

| 1     | 1   | 0   | 1      | 0  | 0   | 1   | 0   | LOGIC 1   |  |

| 1     | 1   | 1   | 1      | 1  | 0   | 1   | 1   | UNDEFINED |  |

<sup>\*</sup>Timing specifications are not guaranteed for D+ and D-.

## Table 3d. Truth Table Receive in Suspend\* (SUSP = 1, $\overline{OE}$ = 1, MODE = X, VPO/VMO = X, ENUM = X)

| INF | PUT | OUTPUT |     |     |                |  |  |

|-----|-----|--------|-----|-----|----------------|--|--|

| D+  | D-  | RCV    | VPI | VMI | RESULT         |  |  |

| 0   | 0   | 0      | 0   | 0   | VPI/VMI ACTIVE |  |  |

| 0   | 1   | 0      | 0   | 1   | VPI/VMI ACTIVE |  |  |

| 1   | 0   | 0      | 1   | 0   | VPI/VMI ACTIVE |  |  |

| 1   | 1   | 0      | 1   | 1   | VPI/VMI ACTIVE |  |  |

<sup>\*</sup>Timing specifications are not guaranteed for D+ and D-.

10 \_\_\_\_\_\_\_/N/1X//V

#### IEC 1000-4-2

The IEC 1000-4-2 standard covers ESD testing and performance of finished equipment; it does not specifically refer to integrated circuits. The MAX3344E/MAX3345E help the user design equipment that meets level 4 of IEC 1000-4-2, without the need for additional ESD-protection components.

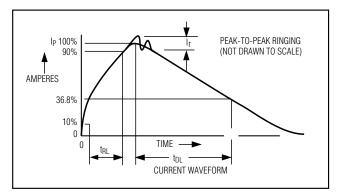

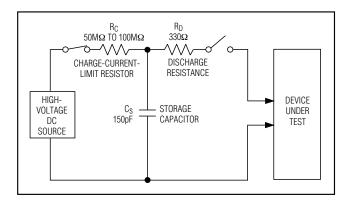

The major difference between tests done using the Human Body Model and IEC 1000-4-2 is a higher peak current in IEC 1000-4-2, because series resistance is lower in the IEC 1000-4-2 model. Hence, the ESD withstand voltage measured to IEC 1000-4-2 is generally lower than that measured using the Human Body Model. Figure 1c shows the IEC 1000-4-2 model.

The Air-Gap Discharge Method involves approaching the device with a charged probe. The Contact Discharge Method connects the probe to the device before the probe is energized.

#### Machine Model

The Machine Model for ESD tests all pins using a 200pF storage capacitor and zero discharge resistance. Its objective is to emulate the stress caused by contact that occurs with handling and assembly during manufacturing. All pins require this protection during manufacturing. Therefore, after PC board assembly, the Machine Model is less relevant to I/O ports.

### Applications Information

### **External Components**

#### **External Resistors**

Two external  $23.7\Omega$  ±1% to  $27.4\Omega$  ±1%, 1/2W resistors are required for USB connection. Place the resistors in between the MAX3344E/MAX3345E and the USB connector on the D+ and D- lines (see the *Typical Operating Circuit*).

### **External Capacitors**

Use three external capacitors for proper operation. Use a 0.1 $\mu$ F ceramic for decoupling V<sub>L</sub>, a 1 $\mu$ F ceramic for decoupling V<sub>CC</sub>, and a 1.0 $\mu$ F (min) ceramic or plastic filter capacitor on VTRM. Return all capacitors to GND.

### **UCSP Applications Information**

For the latest application details on UCSP construction, dimensions, tape carrier information, printed circuit board techniques, bump-pad layout, and recommended reflow temperature profile, as well as the latest information on reliability testing results, refer to the Application Note *UCSP—A Wafer-Level Chip-Scale Package* available on Maxim's website at www.maxim-ic.com/ucsp.

Chip Information

TRANSISTOR COUNT: 2162

PROCESS: BICMOS

Figure 5. D+/D- to RCV, VPI, VMI Propagation Delays

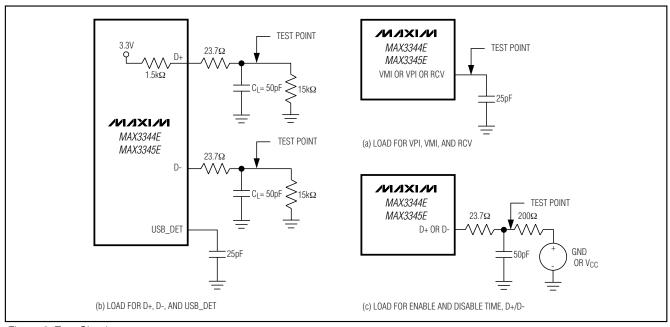

Figure 6. Test Circuits

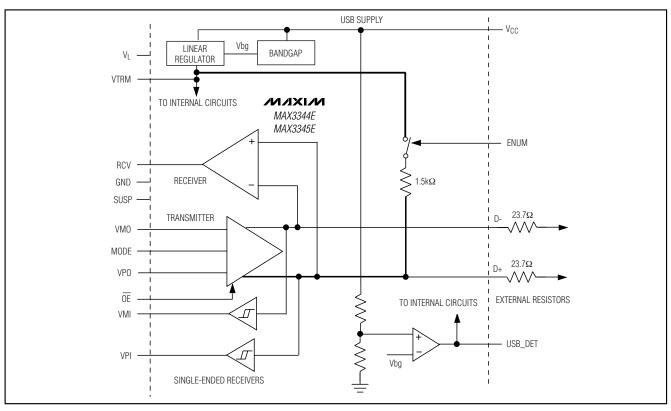

## Functional Diagram

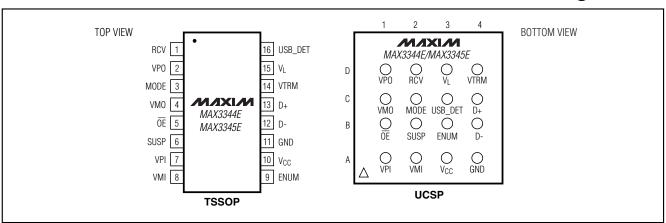

## Pin Configurations

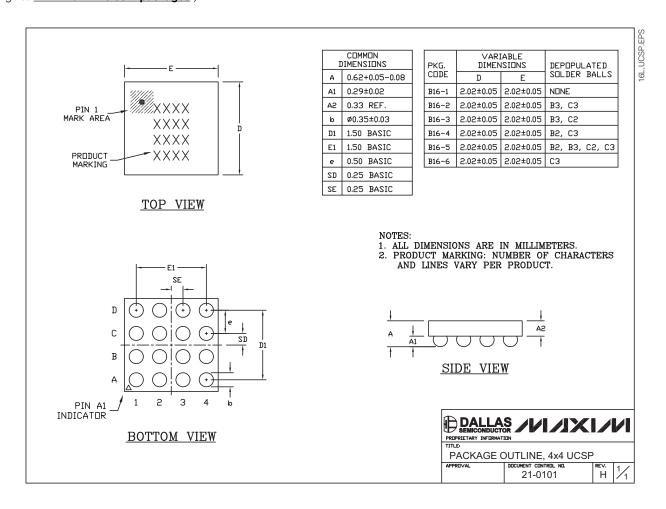

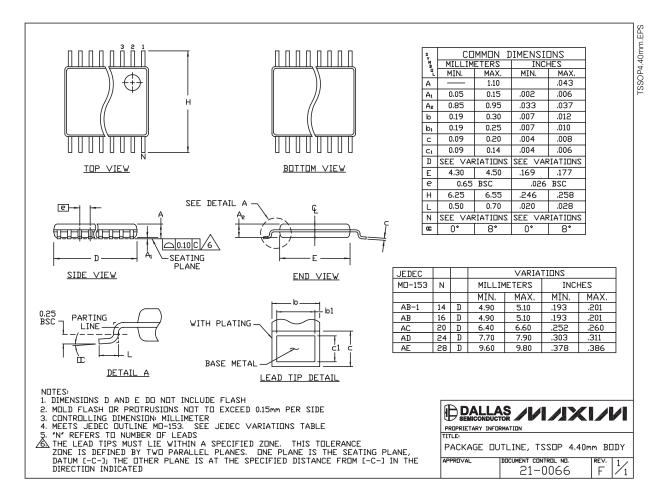

## Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Maxim Integrated:

MAX3344EEUE+ MAX3344EEUE+T MAX3345EEUE+ MAX3345EEUE+T MAX3345EEBE+T